pintest.ino.elf: file format elf32-avr

Disassembly of section .text:

00000000 <__vectors>:

0: 0c 94 34 00 jmp 0x68 ; 0x68 <__ctors_end>

4: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

8: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

c: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

10: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

14: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

18: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

1c: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

20: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

24: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

28: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

2c: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

30: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

34: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

38: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

3c: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

40: 0c 94 19 02 jmp 0x432 ; 0x432 <__vector_16>

44: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

48: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

4c: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

50: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

54: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

58: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

5c: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

60: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

64: 0c 94 51 00 jmp 0xa2 ; 0xa2 <__bad_interrupt>

00000068 <__ctors_end>:

68: 11 24 eor r1, r1

6a: 1f be out 0x3f, r1 ; 63

6c: cf ef ldi r28, 0xFF ; 255

6e: d8 e0 ldi r29, 0x08 ; 8

70: de bf out 0x3e, r29 ; 62

72: cd bf out 0x3d, r28 ; 61

00000074 <__do_copy_data>:

74: 11 e0 ldi r17, 0x01 ; 1

76: a0 e0 ldi r26, 0x00 ; 0

78: b1 e0 ldi r27, 0x01 ; 1

7a: e4 e8 ldi r30, 0x84 ; 132

7c: f5 e0 ldi r31, 0x05 ; 5

7e: 02 c0 rjmp .+4 ; 0x84 <__do_copy_data+0x10>

80: 05 90 lpm r0, Z+

82: 0d 92 st X+, r0

84: a0 30 cpi r26, 0x00 ; 0

86: b1 07 cpc r27, r17

88: d9 f7 brne .-10 ; 0x80 <__do_copy_data+0xc>

0000008a <__do_clear_bss>:

8a: 21 e0 ldi r18, 0x01 ; 1

8c: a0 e0 ldi r26, 0x00 ; 0

8e: b1 e0 ldi r27, 0x01 ; 1

90: 01 c0 rjmp .+2 ; 0x94 <.do_clear_bss_start>

00000092 <.do_clear_bss_loop>:

92: 1d 92 st X+, r1

00000094 <.do_clear_bss_start>:

94: a9 30 cpi r26, 0x09 ; 9

96: b2 07 cpc r27, r18

98: e1 f7 brne .-8 ; 0x92 <.do_clear_bss_loop>

9a: 0e 94 ad 02 call 0x55a ; 0x55a <main>

9e: 0c 94 c0 02 jmp 0x580 ; 0x580 <_exit>

000000a2 <__bad_interrupt>:

a2: 0c 94 00 00 jmp 0 ; 0x0 <__vectors>

000000a6 <__empty>:

* libraries or sketches that supports cooperative threads.

*

* Its defined as a weak symbol and it can be redefined to implement a

* real cooperative scheduler.

*/

static void __empty() {

a6: cf 93 push r28

a8: df 93 push r29

aa: cd b7 in r28, 0x3d ; 61

ac: de b7 in r29, 0x3e ; 62

// Empty

}

ae: df 91 pop r29

b0: cf 91 pop r28

b2: 08 95 ret

000000b4 <_Z8setupUSBv>:

// May be redefined by variant files.

void initVariant() __attribute__((weak));

void initVariant() { }

void setupUSB() __attribute__((weak));

void setupUSB() { }

b4: cf 93 push r28

b6: df 93 push r29

b8: cd b7 in r28, 0x3d ; 61

ba: de b7 in r29, 0x3e ; 62

bc: df 91 pop r29

be: cf 91 pop r28

c0: 08 95 ret

000000c2 <initVariant>:

int atexit(void (* /*func*/ )()) { return 0; }

// Weak empty variant initialization function.

// May be redefined by variant files.

void initVariant() __attribute__((weak));

void initVariant() { }

c2: cf 93 push r28

c4: df 93 push r29

c6: cd b7 in r28, 0x3d ; 61

c8: de b7 in r29, 0x3e ; 62

ca: df 91 pop r29

cc: cf 91 pop r28

ce: 08 95 ret

000000d0 <atexit>:

*/

#include <Arduino.h>

// Declared weak in Arduino.h to allow user redefinitions.

int atexit(void (* /*func*/ )()) { return 0; }

d0: cf 93 push r28

d2: df 93 push r29

d4: 00 d0 rcall .+0 ; 0xd6 <atexit+0x6>

d6: cd b7 in r28, 0x3d ; 61

d8: de b7 in r29, 0x3e ; 62

da: 9a 83 std Y+2, r25 ; 0x02

dc: 89 83 std Y+1, r24 ; 0x01

de: 80 e0 ldi r24, 0x00 ; 0

e0: 90 e0 ldi r25, 0x00 ; 0

e2: 0f 90 pop r0

e4: 0f 90 pop r0

e6: df 91 pop r29

e8: cf 91 pop r28

ea: 08 95 ret

000000ec <init>:

);

// return = 4 cycles

}

void init()

{

ec: cf 93 push r28

ee: df 93 push r29

f0: cd b7 in r28, 0x3d ; 61

f2: de b7 in r29, 0x3e ; 62

// this needs to be called before setup() or some functions won't

// work there

sei();

f4: 78 94 sei

// on the ATmega168, timer 0 is also used for fast hardware pwm

// (using phase-correct PWM would mean that timer 0 overflowed half as often

// resulting in different millis() behavior on the ATmega8 and ATmega168)

#if defined(TCCR0A) && defined(WGM01)

sbi(TCCR0A, WGM01);

f6: 84 e4 ldi r24, 0x44 ; 68

f8: 90 e0 ldi r25, 0x00 ; 0

fa: fc 01 movw r30, r24

fc: 20 81 ld r18, Z

fe: 84 e4 ldi r24, 0x44 ; 68

100: 90 e0 ldi r25, 0x00 ; 0

102: 22 60 ori r18, 0x02 ; 2

104: fc 01 movw r30, r24

106: 20 83 st Z, r18

sbi(TCCR0A, WGM00);

108: 84 e4 ldi r24, 0x44 ; 68

10a: 90 e0 ldi r25, 0x00 ; 0

10c: fc 01 movw r30, r24

10e: 20 81 ld r18, Z

110: 84 e4 ldi r24, 0x44 ; 68

112: 90 e0 ldi r25, 0x00 ; 0

114: 21 60 ori r18, 0x01 ; 1

116: fc 01 movw r30, r24

118: 20 83 st Z, r18

// this combination is for the standard atmega8

sbi(TCCR0, CS01);

sbi(TCCR0, CS00);

#elif defined(TCCR0B) && defined(CS01) && defined(CS00)

// this combination is for the standard 168/328/1280/2560

sbi(TCCR0B, CS01);

11a: 85 e4 ldi r24, 0x45 ; 69

11c: 90 e0 ldi r25, 0x00 ; 0

11e: fc 01 movw r30, r24

120: 20 81 ld r18, Z

122: 85 e4 ldi r24, 0x45 ; 69

124: 90 e0 ldi r25, 0x00 ; 0

126: 22 60 ori r18, 0x02 ; 2

128: fc 01 movw r30, r24

12a: 20 83 st Z, r18

sbi(TCCR0B, CS00);

12c: 85 e4 ldi r24, 0x45 ; 69

12e: 90 e0 ldi r25, 0x00 ; 0

130: fc 01 movw r30, r24

132: 20 81 ld r18, Z

134: 85 e4 ldi r24, 0x45 ; 69

136: 90 e0 ldi r25, 0x00 ; 0

138: 21 60 ori r18, 0x01 ; 1

13a: fc 01 movw r30, r24

13c: 20 83 st Z, r18

// enable timer 0 overflow interrupt

#if defined(TIMSK) && defined(TOIE0)

sbi(TIMSK, TOIE0);

#elif defined(TIMSK0) && defined(TOIE0)

sbi(TIMSK0, TOIE0);

13e: 8e e6 ldi r24, 0x6E ; 110

140: 90 e0 ldi r25, 0x00 ; 0

142: fc 01 movw r30, r24

144: 20 81 ld r18, Z

146: 8e e6 ldi r24, 0x6E ; 110

148: 90 e0 ldi r25, 0x00 ; 0

14a: 21 60 ori r18, 0x01 ; 1

14c: fc 01 movw r30, r24

14e: 20 83 st Z, r18

// this is better for motors as it ensures an even waveform

// note, however, that fast pwm mode can achieve a frequency of up

// 8 MHz (with a 16 MHz clock) at 50% duty cycle

#if defined(TCCR1B) && defined(CS11) && defined(CS10)

TCCR1B = 0;

150: 81 e8 ldi r24, 0x81 ; 129

152: 90 e0 ldi r25, 0x00 ; 0

154: fc 01 movw r30, r24

156: 10 82 st Z, r1

// set timer 1 prescale factor to 64

sbi(TCCR1B, CS11);

158: 81 e8 ldi r24, 0x81 ; 129

15a: 90 e0 ldi r25, 0x00 ; 0

15c: fc 01 movw r30, r24

15e: 20 81 ld r18, Z

160: 81 e8 ldi r24, 0x81 ; 129

162: 90 e0 ldi r25, 0x00 ; 0

164: 22 60 ori r18, 0x02 ; 2

166: fc 01 movw r30, r24

168: 20 83 st Z, r18

#if F_CPU >= 8000000L

sbi(TCCR1B, CS10);

16a: 81 e8 ldi r24, 0x81 ; 129

16c: 90 e0 ldi r25, 0x00 ; 0

16e: fc 01 movw r30, r24

170: 20 81 ld r18, Z

172: 81 e8 ldi r24, 0x81 ; 129

174: 90 e0 ldi r25, 0x00 ; 0

176: 21 60 ori r18, 0x01 ; 1

178: fc 01 movw r30, r24

17a: 20 83 st Z, r18

sbi(TCCR1, CS10);

#endif

#endif

// put timer 1 in 8-bit phase correct pwm mode

#if defined(TCCR1A) && defined(WGM10)

sbi(TCCR1A, WGM10);

17c: 80 e8 ldi r24, 0x80 ; 128

17e: 90 e0 ldi r25, 0x00 ; 0

180: fc 01 movw r30, r24

182: 20 81 ld r18, Z

184: 80 e8 ldi r24, 0x80 ; 128

186: 90 e0 ldi r25, 0x00 ; 0

188: 21 60 ori r18, 0x01 ; 1

18a: fc 01 movw r30, r24

18c: 20 83 st Z, r18

// set timer 2 prescale factor to 64

#if defined(TCCR2) && defined(CS22)

sbi(TCCR2, CS22);

#elif defined(TCCR2B) && defined(CS22)

sbi(TCCR2B, CS22);

18e: 81 eb ldi r24, 0xB1 ; 177

190: 90 e0 ldi r25, 0x00 ; 0

192: fc 01 movw r30, r24

194: 20 81 ld r18, Z

196: 81 eb ldi r24, 0xB1 ; 177

198: 90 e0 ldi r25, 0x00 ; 0

19a: 24 60 ori r18, 0x04 ; 4

19c: fc 01 movw r30, r24

19e: 20 83 st Z, r18

// configure timer 2 for phase correct pwm (8-bit)

#if defined(TCCR2) && defined(WGM20)

sbi(TCCR2, WGM20);

#elif defined(TCCR2A) && defined(WGM20)

sbi(TCCR2A, WGM20);

1a0: 80 eb ldi r24, 0xB0 ; 176

1a2: 90 e0 ldi r25, 0x00 ; 0

1a4: fc 01 movw r30, r24

1a6: 20 81 ld r18, Z

1a8: 80 eb ldi r24, 0xB0 ; 176

1aa: 90 e0 ldi r25, 0x00 ; 0

1ac: 21 60 ori r18, 0x01 ; 1

1ae: fc 01 movw r30, r24

1b0: 20 83 st Z, r18

#endif

#if defined(ADCSRA)

// set a2d prescaler so we are inside the desired 50-200 KHz range.

#if F_CPU >= 16000000 // 16 MHz / 128 = 125 KHz

sbi(ADCSRA, ADPS2);

1b2: 8a e7 ldi r24, 0x7A ; 122

1b4: 90 e0 ldi r25, 0x00 ; 0

1b6: fc 01 movw r30, r24

1b8: 20 81 ld r18, Z

1ba: 8a e7 ldi r24, 0x7A ; 122

1bc: 90 e0 ldi r25, 0x00 ; 0

1be: 24 60 ori r18, 0x04 ; 4

1c0: fc 01 movw r30, r24

1c2: 20 83 st Z, r18

sbi(ADCSRA, ADPS1);

1c4: 8a e7 ldi r24, 0x7A ; 122

1c6: 90 e0 ldi r25, 0x00 ; 0

1c8: fc 01 movw r30, r24

1ca: 20 81 ld r18, Z

1cc: 8a e7 ldi r24, 0x7A ; 122

1ce: 90 e0 ldi r25, 0x00 ; 0

1d0: 22 60 ori r18, 0x02 ; 2

1d2: fc 01 movw r30, r24

1d4: 20 83 st Z, r18

sbi(ADCSRA, ADPS0);

1d6: 8a e7 ldi r24, 0x7A ; 122

1d8: 90 e0 ldi r25, 0x00 ; 0

1da: fc 01 movw r30, r24

1dc: 20 81 ld r18, Z

1de: 8a e7 ldi r24, 0x7A ; 122

1e0: 90 e0 ldi r25, 0x00 ; 0

1e2: 21 60 ori r18, 0x01 ; 1

1e4: fc 01 movw r30, r24

1e6: 20 83 st Z, r18

cbi(ADCSRA, ADPS2);

cbi(ADCSRA, ADPS1);

sbi(ADCSRA, ADPS0);

#endif

// enable a2d conversions

sbi(ADCSRA, ADEN);

1e8: 8a e7 ldi r24, 0x7A ; 122

1ea: 90 e0 ldi r25, 0x00 ; 0

1ec: fc 01 movw r30, r24

1ee: 20 81 ld r18, Z

1f0: 8a e7 ldi r24, 0x7A ; 122

1f2: 90 e0 ldi r25, 0x00 ; 0

1f4: 20 68 ori r18, 0x80 ; 128

1f6: fc 01 movw r30, r24

1f8: 20 83 st Z, r18

// here so they can be used as normal digital i/o; they will be

// reconnected in Serial.begin()

#if defined(UCSRB)

UCSRB = 0;

#elif defined(UCSR0B)

UCSR0B = 0;

1fa: 81 ec ldi r24, 0xC1 ; 193

1fc: 90 e0 ldi r25, 0x00 ; 0

1fe: fc 01 movw r30, r24

200: 10 82 st Z, r1

#endif

}

202: df 91 pop r29

204: cf 91 pop r28

206: 08 95 ret

00000208 <delayMicroseconds>:

}

}

/* Delay for the given number of microseconds. Assumes a 1, 8, 12, 16, 20 or 24 MHz clock. */

void delayMicroseconds(unsigned int us)

{

208: cf 93 push r28

20a: df 93 push r29

20c: 00 d0 rcall .+0 ; 0x20e <delayMicroseconds+0x6>

20e: cd b7 in r28, 0x3d ; 61

210: de b7 in r29, 0x3e ; 62

212: 9a 83 std Y+2, r25 ; 0x02

214: 89 83 std Y+1, r24 ; 0x01

#elif F_CPU >= 16000000L

// for the 16 MHz clock on most Arduino boards

// for a one-microsecond delay, simply return. the overhead

// of the function call takes 14 (16) cycles, which is 1us

if (us <= 1) return; // = 3 cycles, (4 when true)

216: 89 81 ldd r24, Y+1 ; 0x01

218: 9a 81 ldd r25, Y+2 ; 0x02

21a: 02 97 sbiw r24, 0x02 ; 2

21c: 98 f0 brcs .+38 ; 0x244 <delayMicroseconds+0x3c>

// the following loop takes 1/4 of a microsecond (4 cycles)

// per iteration, so execute it four times for each microsecond of

// delay requested.

us <<= 2; // x4 us, = 4 cycles

21e: 89 81 ldd r24, Y+1 ; 0x01

220: 9a 81 ldd r25, Y+2 ; 0x02

222: 88 0f add r24, r24

224: 99 1f adc r25, r25

226: 88 0f add r24, r24

228: 99 1f adc r25, r25

22a: 9a 83 std Y+2, r25 ; 0x02

22c: 89 83 std Y+1, r24 ; 0x01

// account for the time taken in the preceeding commands.

// we just burned 19 (21) cycles above, remove 5, (5*4=20)

// us is at least 8 so we can substract 5

us -= 5; // = 2 cycles,

22e: 89 81 ldd r24, Y+1 ; 0x01

230: 9a 81 ldd r25, Y+2 ; 0x02

232: 05 97 sbiw r24, 0x05 ; 5

234: 9a 83 std Y+2, r25 ; 0x02

236: 89 83 std Y+1, r24 ; 0x01

#endif

// busy wait

__asm__ __volatile__ (

238: 89 81 ldd r24, Y+1 ; 0x01

23a: 9a 81 ldd r25, Y+2 ; 0x02

23c: 01 97 sbiw r24, 0x01 ; 1

23e: f1 f7 brne .-4 ; 0x23c <delayMicroseconds+0x34>

240: 9a 83 std Y+2, r25 ; 0x02

242: 89 83 std Y+1, r24 ; 0x01

"1: sbiw %0,1" "\n\t" // 2 cycles

"brne 1b" : "=w" (us) : "0" (us) // 2 cycles

);

// return = 4 cycles

}

244: 0f 90 pop r0

246: 0f 90 pop r0

248: df 91 pop r29

24a: cf 91 pop r28

24c: 08 95 ret

0000024e <micros>:

SREG = oldSREG;

return m;

}

unsigned long micros() {

24e: cf 93 push r28

250: df 93 push r29

252: 00 d0 rcall .+0 ; 0x254 <micros+0x6>

254: 00 d0 rcall .+0 ; 0x256 <micros+0x8>

256: 00 d0 rcall .+0 ; 0x258 <micros+0xa>

258: cd b7 in r28, 0x3d ; 61

25a: de b7 in r29, 0x3e ; 62

unsigned long m;

uint8_t oldSREG = SREG, t;

25c: 8f e5 ldi r24, 0x5F ; 95

25e: 90 e0 ldi r25, 0x00 ; 0

260: fc 01 movw r30, r24

262: 80 81 ld r24, Z

264: 8d 83 std Y+5, r24 ; 0x05

cli();

266: f8 94 cli

m = timer0_overflow_count;

268: 80 91 05 01 lds r24, 0x0105 ; 0x800105 <timer0_overflow_count>

26c: 90 91 06 01 lds r25, 0x0106 ; 0x800106 <timer0_overflow_count+0x1>

270: a0 91 07 01 lds r26, 0x0107 ; 0x800107 <timer0_overflow_count+0x2>

274: b0 91 08 01 lds r27, 0x0108 ; 0x800108 <timer0_overflow_count+0x3>

278: 89 83 std Y+1, r24 ; 0x01

27a: 9a 83 std Y+2, r25 ; 0x02

27c: ab 83 std Y+3, r26 ; 0x03

27e: bc 83 std Y+4, r27 ; 0x04

#if defined(TCNT0)

t = TCNT0;

280: 86 e4 ldi r24, 0x46 ; 70

282: 90 e0 ldi r25, 0x00 ; 0

284: fc 01 movw r30, r24

286: 80 81 ld r24, Z

288: 8e 83 std Y+6, r24 ; 0x06

#else

#error TIMER 0 not defined

#endif

#ifdef TIFR0

if ((TIFR0 & _BV(TOV0)) && (t < 255))

28a: 85 e3 ldi r24, 0x35 ; 53

28c: 90 e0 ldi r25, 0x00 ; 0

28e: fc 01 movw r30, r24

290: 80 81 ld r24, Z

292: 88 2f mov r24, r24

294: 90 e0 ldi r25, 0x00 ; 0

296: 81 70 andi r24, 0x01 ; 1

298: 99 27 eor r25, r25

29a: 89 2b or r24, r25

29c: 71 f0 breq .+28 ; 0x2ba <micros+0x6c>

29e: 8e 81 ldd r24, Y+6 ; 0x06

2a0: 8f 3f cpi r24, 0xFF ; 255

2a2: 59 f0 breq .+22 ; 0x2ba <micros+0x6c>

m++;

2a4: 89 81 ldd r24, Y+1 ; 0x01

2a6: 9a 81 ldd r25, Y+2 ; 0x02

2a8: ab 81 ldd r26, Y+3 ; 0x03

2aa: bc 81 ldd r27, Y+4 ; 0x04

2ac: 01 96 adiw r24, 0x01 ; 1

2ae: a1 1d adc r26, r1

2b0: b1 1d adc r27, r1

2b2: 89 83 std Y+1, r24 ; 0x01

2b4: 9a 83 std Y+2, r25 ; 0x02

2b6: ab 83 std Y+3, r26 ; 0x03

2b8: bc 83 std Y+4, r27 ; 0x04

#else

if ((TIFR & _BV(TOV0)) && (t < 255))

m++;

#endif

SREG = oldSREG;

2ba: 8f e5 ldi r24, 0x5F ; 95

2bc: 90 e0 ldi r25, 0x00 ; 0

2be: 2d 81 ldd r18, Y+5 ; 0x05

2c0: fc 01 movw r30, r24

2c2: 20 83 st Z, r18

return ((m << 8) + t) * (64 / clockCyclesPerMicrosecond());

2c4: 89 81 ldd r24, Y+1 ; 0x01

2c6: 9a 81 ldd r25, Y+2 ; 0x02

2c8: ab 81 ldd r26, Y+3 ; 0x03

2ca: bc 81 ldd r27, Y+4 ; 0x04

2cc: 22 27 eor r18, r18

2ce: 38 2f mov r19, r24

2d0: 49 2f mov r20, r25

2d2: 5a 2f mov r21, r26

2d4: 8e 81 ldd r24, Y+6 ; 0x06

2d6: 88 2f mov r24, r24

2d8: 90 e0 ldi r25, 0x00 ; 0

2da: a0 e0 ldi r26, 0x00 ; 0

2dc: b0 e0 ldi r27, 0x00 ; 0

2de: 82 0f add r24, r18

2e0: 93 1f adc r25, r19

2e2: a4 1f adc r26, r20

2e4: b5 1f adc r27, r21

2e6: 88 0f add r24, r24

2e8: 99 1f adc r25, r25

2ea: aa 1f adc r26, r26

2ec: bb 1f adc r27, r27

2ee: 88 0f add r24, r24

2f0: 99 1f adc r25, r25

2f2: aa 1f adc r26, r26

2f4: bb 1f adc r27, r27

}

2f6: bc 01 movw r22, r24

2f8: cd 01 movw r24, r26

2fa: 26 96 adiw r28, 0x06 ; 6

2fc: 0f b6 in r0, 0x3f ; 63

2fe: f8 94 cli

300: de bf out 0x3e, r29 ; 62

302: 0f be out 0x3f, r0 ; 63

304: cd bf out 0x3d, r28 ; 61

306: df 91 pop r29

308: cf 91 pop r28

30a: 08 95 ret

0000030c <delay>:

void delay(unsigned long ms)

{

30c: ef 92 push r14

30e: ff 92 push r15

310: 0f 93 push r16

312: 1f 93 push r17

314: cf 93 push r28

316: df 93 push r29

318: cd b7 in r28, 0x3d ; 61

31a: de b7 in r29, 0x3e ; 62

31c: 28 97 sbiw r28, 0x08 ; 8

31e: 0f b6 in r0, 0x3f ; 63

320: f8 94 cli

322: de bf out 0x3e, r29 ; 62

324: 0f be out 0x3f, r0 ; 63

326: cd bf out 0x3d, r28 ; 61

328: 6d 83 std Y+5, r22 ; 0x05

32a: 7e 83 std Y+6, r23 ; 0x06

32c: 8f 83 std Y+7, r24 ; 0x07

32e: 98 87 std Y+8, r25 ; 0x08

uint32_t start = micros();

330: 0e 94 27 01 call 0x24e ; 0x24e <micros>

334: dc 01 movw r26, r24

336: cb 01 movw r24, r22

338: 89 83 std Y+1, r24 ; 0x01

33a: 9a 83 std Y+2, r25 ; 0x02

33c: ab 83 std Y+3, r26 ; 0x03

33e: bc 83 std Y+4, r27 ; 0x04

340: 37 c0 rjmp .+110 ; 0x3b0 <delay+0xa4>

while (ms > 0) {

yield();

342: 0e 94 53 00 call 0xa6 ; 0xa6 <__empty>

346: 17 c0 rjmp .+46 ; 0x376 <delay+0x6a>

while ( ms > 0 && (micros() - start) >= 1000) {

ms--;

348: 8d 81 ldd r24, Y+5 ; 0x05

34a: 9e 81 ldd r25, Y+6 ; 0x06

34c: af 81 ldd r26, Y+7 ; 0x07

34e: b8 85 ldd r27, Y+8 ; 0x08

350: 01 97 sbiw r24, 0x01 ; 1

352: a1 09 sbc r26, r1

354: b1 09 sbc r27, r1

356: 8d 83 std Y+5, r24 ; 0x05

358: 9e 83 std Y+6, r25 ; 0x06

35a: af 83 std Y+7, r26 ; 0x07

35c: b8 87 std Y+8, r27 ; 0x08

start += 1000;

35e: 89 81 ldd r24, Y+1 ; 0x01

360: 9a 81 ldd r25, Y+2 ; 0x02

362: ab 81 ldd r26, Y+3 ; 0x03

364: bc 81 ldd r27, Y+4 ; 0x04

366: 88 51 subi r24, 0x18 ; 24

368: 9c 4f sbci r25, 0xFC ; 252

36a: af 4f sbci r26, 0xFF ; 255

36c: bf 4f sbci r27, 0xFF ; 255

36e: 89 83 std Y+1, r24 ; 0x01

370: 9a 83 std Y+2, r25 ; 0x02

372: ab 83 std Y+3, r26 ; 0x03

374: bc 83 std Y+4, r27 ; 0x04

{

uint32_t start = micros();

while (ms > 0) {

yield();

while ( ms > 0 && (micros() - start) >= 1000) {

376: 8d 81 ldd r24, Y+5 ; 0x05

378: 9e 81 ldd r25, Y+6 ; 0x06

37a: af 81 ldd r26, Y+7 ; 0x07

37c: b8 85 ldd r27, Y+8 ; 0x08

37e: 89 2b or r24, r25

380: 8a 2b or r24, r26

382: 8b 2b or r24, r27

384: a9 f0 breq .+42 ; 0x3b0 <delay+0xa4>

386: 0e 94 27 01 call 0x24e ; 0x24e <micros>

38a: 9b 01 movw r18, r22

38c: ac 01 movw r20, r24

38e: 89 81 ldd r24, Y+1 ; 0x01

390: 9a 81 ldd r25, Y+2 ; 0x02

392: ab 81 ldd r26, Y+3 ; 0x03

394: bc 81 ldd r27, Y+4 ; 0x04

396: 79 01 movw r14, r18

398: 8a 01 movw r16, r20

39a: e8 1a sub r14, r24

39c: f9 0a sbc r15, r25

39e: 0a 0b sbc r16, r26

3a0: 1b 0b sbc r17, r27

3a2: d8 01 movw r26, r16

3a4: c7 01 movw r24, r14

3a6: 88 3e cpi r24, 0xE8 ; 232

3a8: 93 40 sbci r25, 0x03 ; 3

3aa: a1 05 cpc r26, r1

3ac: b1 05 cpc r27, r1

3ae: 60 f6 brcc .-104 ; 0x348 <delay+0x3c>

void delay(unsigned long ms)

{

uint32_t start = micros();

while (ms > 0) {

3b0: 8d 81 ldd r24, Y+5 ; 0x05

3b2: 9e 81 ldd r25, Y+6 ; 0x06

3b4: af 81 ldd r26, Y+7 ; 0x07

3b6: b8 85 ldd r27, Y+8 ; 0x08

3b8: 89 2b or r24, r25

3ba: 8a 2b or r24, r26

3bc: 8b 2b or r24, r27

3be: 09 f6 brne .-126 ; 0x342 <delay+0x36>

while ( ms > 0 && (micros() - start) >= 1000) {

ms--;

start += 1000;

}

}

}

3c0: 28 96 adiw r28, 0x08 ; 8

3c2: 0f b6 in r0, 0x3f ; 63

3c4: f8 94 cli

3c6: de bf out 0x3e, r29 ; 62

3c8: 0f be out 0x3f, r0 ; 63

3ca: cd bf out 0x3d, r28 ; 61

3cc: df 91 pop r29

3ce: cf 91 pop r28

3d0: 1f 91 pop r17

3d2: 0f 91 pop r16

3d4: ff 90 pop r15

3d6: ef 90 pop r14

3d8: 08 95 ret

000003da <millis>:

timer0_millis = m;

timer0_overflow_count++;

}

unsigned long millis()

{

3da: cf 93 push r28

3dc: df 93 push r29

3de: 00 d0 rcall .+0 ; 0x3e0 <millis+0x6>

3e0: 00 d0 rcall .+0 ; 0x3e2 <millis+0x8>

3e2: 1f 92 push r1

3e4: cd b7 in r28, 0x3d ; 61

3e6: de b7 in r29, 0x3e ; 62

unsigned long m;

uint8_t oldSREG = SREG;

3e8: 8f e5 ldi r24, 0x5F ; 95

3ea: 90 e0 ldi r25, 0x00 ; 0

3ec: fc 01 movw r30, r24

3ee: 80 81 ld r24, Z

3f0: 89 83 std Y+1, r24 ; 0x01

// disable interrupts while we read timer0_millis or we might get an

// inconsistent value (e.g. in the middle of a write to timer0_millis)

cli();

3f2: f8 94 cli

m = timer0_millis;

3f4: 80 91 01 01 lds r24, 0x0101 ; 0x800101 <timer0_millis>

3f8: 90 91 02 01 lds r25, 0x0102 ; 0x800102 <timer0_millis+0x1>

3fc: a0 91 03 01 lds r26, 0x0103 ; 0x800103 <timer0_millis+0x2>

400: b0 91 04 01 lds r27, 0x0104 ; 0x800104 <timer0_millis+0x3>

404: 8a 83 std Y+2, r24 ; 0x02

406: 9b 83 std Y+3, r25 ; 0x03

408: ac 83 std Y+4, r26 ; 0x04

40a: bd 83 std Y+5, r27 ; 0x05

SREG = oldSREG;

40c: 8f e5 ldi r24, 0x5F ; 95

40e: 90 e0 ldi r25, 0x00 ; 0

410: 29 81 ldd r18, Y+1 ; 0x01

412: fc 01 movw r30, r24

414: 20 83 st Z, r18

return m;

416: 8a 81 ldd r24, Y+2 ; 0x02

418: 9b 81 ldd r25, Y+3 ; 0x03

41a: ac 81 ldd r26, Y+4 ; 0x04

41c: bd 81 ldd r27, Y+5 ; 0x05

}

41e: bc 01 movw r22, r24

420: cd 01 movw r24, r26

422: 0f 90 pop r0

424: 0f 90 pop r0

426: 0f 90 pop r0

428: 0f 90 pop r0

42a: 0f 90 pop r0

42c: df 91 pop r29

42e: cf 91 pop r28

430: 08 95 ret

00000432 <__vector_16>:

#if defined(TIM0_OVF_vect)

ISR(TIM0_OVF_vect)

#else

ISR(TIMER0_OVF_vect)

#endif

{

432: 1f 92 push r1

434: 0f 92 push r0

436: 0f b6 in r0, 0x3f ; 63

438: 0f 92 push r0

43a: 11 24 eor r1, r1

43c: 8f 93 push r24

43e: 9f 93 push r25

440: af 93 push r26

442: bf 93 push r27

444: cf 93 push r28

446: df 93 push r29

448: cd b7 in r28, 0x3d ; 61

44a: de b7 in r29, 0x3e ; 62

44c: 25 97 sbiw r28, 0x05 ; 5

44e: de bf out 0x3e, r29 ; 62

450: cd bf out 0x3d, r28 ; 61

// copy these to local variables so they can be stored in registers

// (volatile variables must be read from memory on every access)

unsigned long m = timer0_millis;

452: 80 91 01 01 lds r24, 0x0101 ; 0x800101 <timer0_millis>

456: 90 91 02 01 lds r25, 0x0102 ; 0x800102 <timer0_millis+0x1>

45a: a0 91 03 01 lds r26, 0x0103 ; 0x800103 <timer0_millis+0x2>

45e: b0 91 04 01 lds r27, 0x0104 ; 0x800104 <timer0_millis+0x3>

462: 89 83 std Y+1, r24 ; 0x01

464: 9a 83 std Y+2, r25 ; 0x02

466: ab 83 std Y+3, r26 ; 0x03

468: bc 83 std Y+4, r27 ; 0x04

unsigned char f = timer0_fract;

46a: 80 91 00 01 lds r24, 0x0100 ; 0x800100 <__data_end>

46e: 8d 83 std Y+5, r24 ; 0x05

m += MILLIS_INC;

470: 89 81 ldd r24, Y+1 ; 0x01

472: 9a 81 ldd r25, Y+2 ; 0x02

474: ab 81 ldd r26, Y+3 ; 0x03

476: bc 81 ldd r27, Y+4 ; 0x04

478: 01 96 adiw r24, 0x01 ; 1

47a: a1 1d adc r26, r1

47c: b1 1d adc r27, r1

47e: 89 83 std Y+1, r24 ; 0x01

480: 9a 83 std Y+2, r25 ; 0x02

482: ab 83 std Y+3, r26 ; 0x03

484: bc 83 std Y+4, r27 ; 0x04

f += FRACT_INC;

486: 8d 81 ldd r24, Y+5 ; 0x05

488: 8d 5f subi r24, 0xFD ; 253

48a: 8d 83 std Y+5, r24 ; 0x05

if (f >= FRACT_MAX) {

48c: 8d 81 ldd r24, Y+5 ; 0x05

48e: 8d 37 cpi r24, 0x7D ; 125

490: 70 f0 brcs .+28 ; 0x4ae <__vector_16+0x7c>

f -= FRACT_MAX;

492: 8d 81 ldd r24, Y+5 ; 0x05

494: 8d 57 subi r24, 0x7D ; 125

496: 8d 83 std Y+5, r24 ; 0x05

m += 1;

498: 89 81 ldd r24, Y+1 ; 0x01

49a: 9a 81 ldd r25, Y+2 ; 0x02

49c: ab 81 ldd r26, Y+3 ; 0x03

49e: bc 81 ldd r27, Y+4 ; 0x04

4a0: 01 96 adiw r24, 0x01 ; 1

4a2: a1 1d adc r26, r1

4a4: b1 1d adc r27, r1

4a6: 89 83 std Y+1, r24 ; 0x01

4a8: 9a 83 std Y+2, r25 ; 0x02

4aa: ab 83 std Y+3, r26 ; 0x03

4ac: bc 83 std Y+4, r27 ; 0x04

}

timer0_fract = f;

4ae: 8d 81 ldd r24, Y+5 ; 0x05

4b0: 80 93 00 01 sts 0x0100, r24 ; 0x800100 <__data_end>

timer0_millis = m;

4b4: 89 81 ldd r24, Y+1 ; 0x01

4b6: 9a 81 ldd r25, Y+2 ; 0x02

4b8: ab 81 ldd r26, Y+3 ; 0x03

4ba: bc 81 ldd r27, Y+4 ; 0x04

4bc: 80 93 01 01 sts 0x0101, r24 ; 0x800101 <timer0_millis>

4c0: 90 93 02 01 sts 0x0102, r25 ; 0x800102 <timer0_millis+0x1>

4c4: a0 93 03 01 sts 0x0103, r26 ; 0x800103 <timer0_millis+0x2>

4c8: b0 93 04 01 sts 0x0104, r27 ; 0x800104 <timer0_millis+0x3>

timer0_overflow_count++;

4cc: 80 91 05 01 lds r24, 0x0105 ; 0x800105 <timer0_overflow_count>

4d0: 90 91 06 01 lds r25, 0x0106 ; 0x800106 <timer0_overflow_count+0x1>

4d4: a0 91 07 01 lds r26, 0x0107 ; 0x800107 <timer0_overflow_count+0x2>

4d8: b0 91 08 01 lds r27, 0x0108 ; 0x800108 <timer0_overflow_count+0x3>

4dc: 01 96 adiw r24, 0x01 ; 1

4de: a1 1d adc r26, r1

4e0: b1 1d adc r27, r1

4e2: 80 93 05 01 sts 0x0105, r24 ; 0x800105 <timer0_overflow_count>

4e6: 90 93 06 01 sts 0x0106, r25 ; 0x800106 <timer0_overflow_count+0x1>

4ea: a0 93 07 01 sts 0x0107, r26 ; 0x800107 <timer0_overflow_count+0x2>

4ee: b0 93 08 01 sts 0x0108, r27 ; 0x800108 <timer0_overflow_count+0x3>

}

4f2: 0f 90 pop r0

4f4: 0f 90 pop r0

4f6: 0f 90 pop r0

4f8: 0f 90 pop r0

4fa: 0f 90 pop r0

4fc: df 91 pop r29

4fe: cf 91 pop r28

500: bf 91 pop r27

502: af 91 pop r26

504: 9f 91 pop r25

506: 8f 91 pop r24

508: 0f 90 pop r0

50a: 0f be out 0x3f, r0 ; 63

50c: 0f 90 pop r0

50e: 1f 90 pop r1

510: 18 95 reti

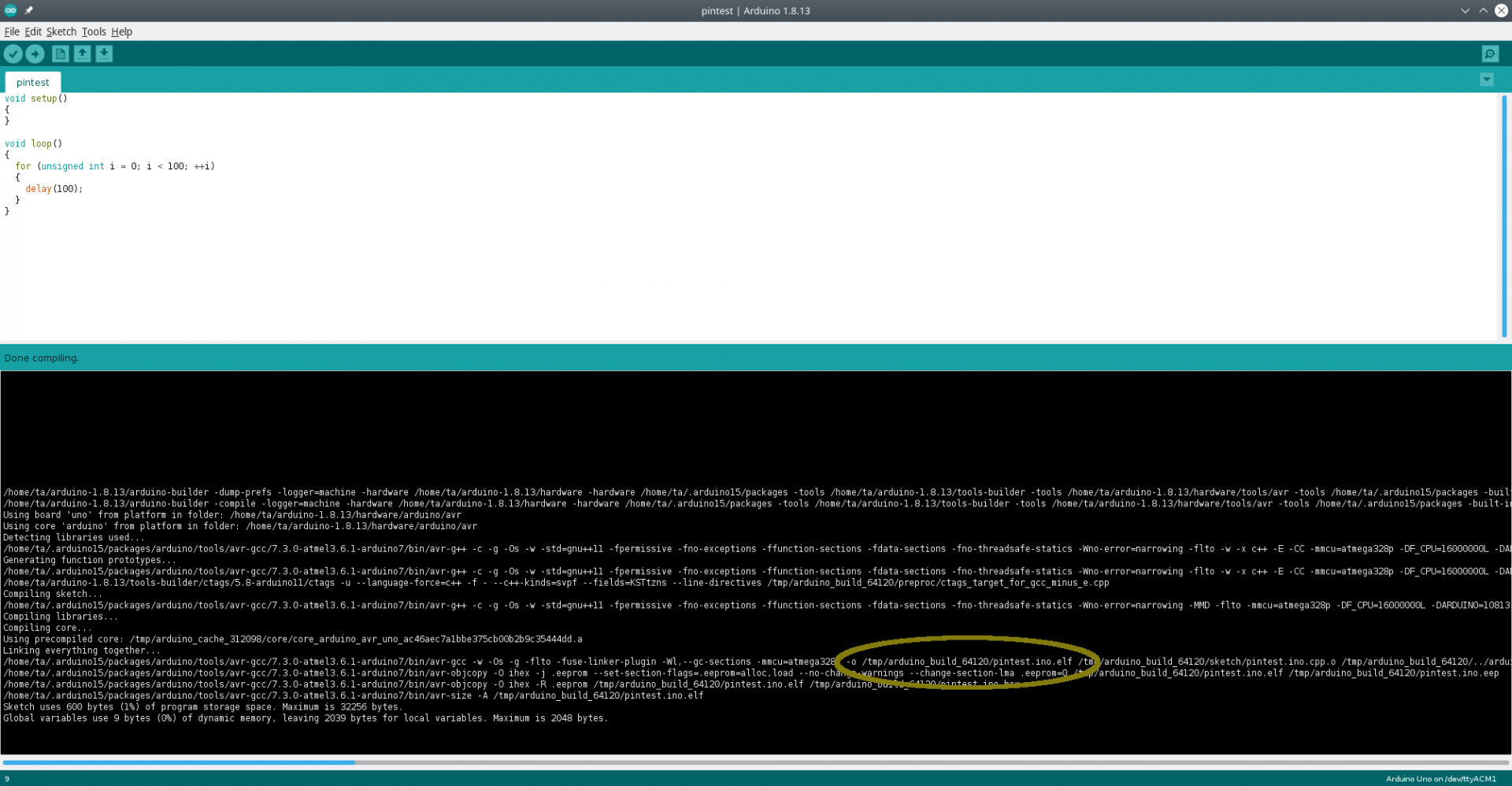

00000512 <loop>:

void setup()

{

}

void loop()

{

512: cf 93 push r28

514: df 93 push r29

516: 00 d0 rcall .+0 ; 0x518 <loop+0x6>

518: cd b7 in r28, 0x3d ; 61

51a: de b7 in r29, 0x3e ; 62

for (unsigned int i = 0; i < 100; ++i)

51c: 1a 82 std Y+2, r1 ; 0x02

51e: 19 82 std Y+1, r1 ; 0x01

520: 89 81 ldd r24, Y+1 ; 0x01

522: 9a 81 ldd r25, Y+2 ; 0x02

524: 84 36 cpi r24, 0x64 ; 100

526: 91 05 cpc r25, r1

528: 60 f4 brcc .+24 ; 0x542 <loop+0x30>

{

delay(100);

52a: 64 e6 ldi r22, 0x64 ; 100

52c: 70 e0 ldi r23, 0x00 ; 0

52e: 80 e0 ldi r24, 0x00 ; 0

530: 90 e0 ldi r25, 0x00 ; 0

532: 0e 94 86 01 call 0x30c ; 0x30c <delay>

{

}

void loop()

{

for (unsigned int i = 0; i < 100; ++i)

536: 89 81 ldd r24, Y+1 ; 0x01

538: 9a 81 ldd r25, Y+2 ; 0x02

53a: 01 96 adiw r24, 0x01 ; 1

53c: 9a 83 std Y+2, r25 ; 0x02

53e: 89 83 std Y+1, r24 ; 0x01

540: ef cf rjmp .-34 ; 0x520 <loop+0xe>

{

delay(100);

}

}

542: 0f 90 pop r0

544: 0f 90 pop r0

546: df 91 pop r29

548: cf 91 pop r28

54a: 08 95 ret

0000054c <setup>:

void setup()

{

54c: cf 93 push r28

54e: df 93 push r29

550: cd b7 in r28, 0x3d ; 61

552: de b7 in r29, 0x3e ; 62

}

554: df 91 pop r29

556: cf 91 pop r28

558: 08 95 ret

0000055a <main>:

void setupUSB() __attribute__((weak));

void setupUSB() { }

int main(void)

{

55a: cf 93 push r28

55c: df 93 push r29

55e: cd b7 in r28, 0x3d ; 61

560: de b7 in r29, 0x3e ; 62

init();

562: 0e 94 76 00 call 0xec ; 0xec <init>

initVariant();

566: 0e 94 61 00 call 0xc2 ; 0xc2 <initVariant>

#if defined(USBCON)

USBDevice.attach();

#endif

setup();

56a: 0e 94 a6 02 call 0x54c ; 0x54c <setup>

for (;;) {

loop();

56e: 0e 94 89 02 call 0x512 ; 0x512 <loop>

if (serialEventRun) serialEventRun();

572: 80 e0 ldi r24, 0x00 ; 0

574: 90 e0 ldi r25, 0x00 ; 0

576: 89 2b or r24, r25

578: d1 f3 breq .-12 ; 0x56e <main+0x14>

57a: 0e 94 00 00 call 0 ; 0x0 <__vectors>

57e: f7 cf rjmp .-18 ; 0x56e <main+0x14>

00000580 <_exit>:

580: f8 94 cli

00000582 <__stop_program>:

582: ff cf rjmp .-2 ; 0x582 <__stop_program>