doktor_balon

Yeni Üye

- Katılım

- 11 Kasım 2022

- Mesajlar

- 8

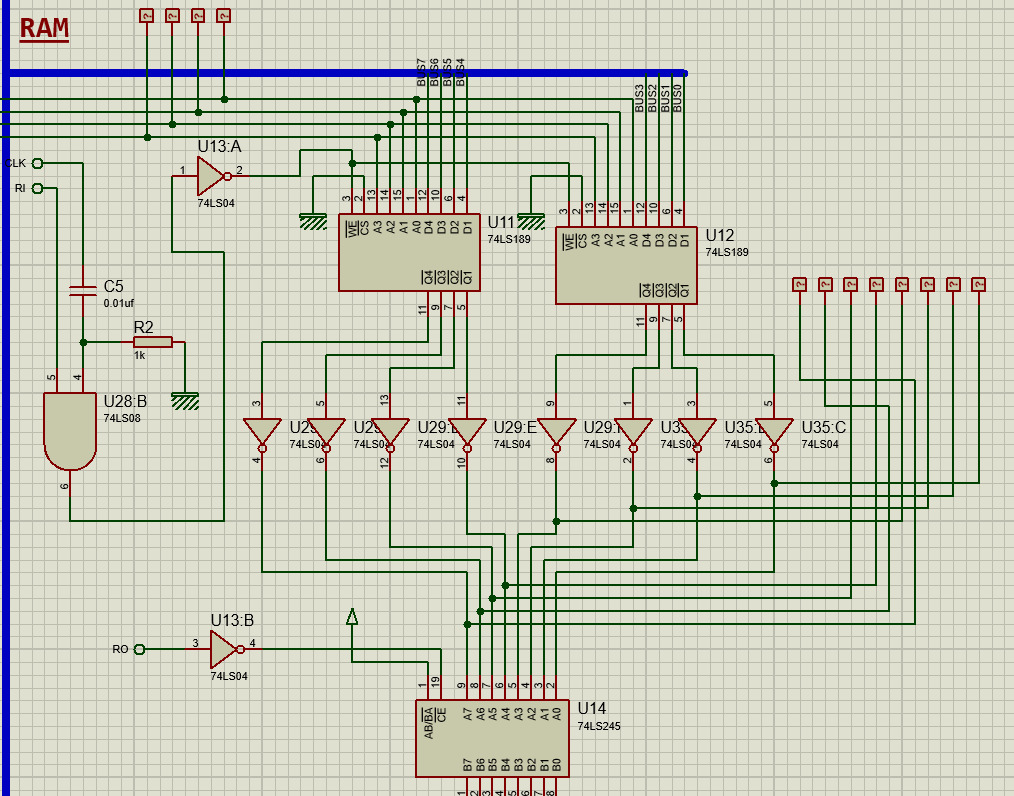

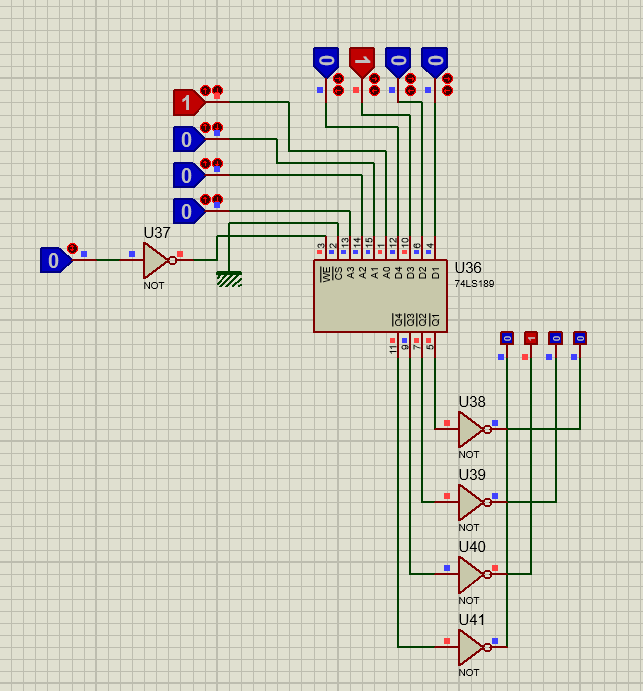

Proteus 8 üzerinden bir devre oluşturuyorum. Devrede 16 tane 4 bit tutan 74ls189 dan ikitane kullandım amacım: clock sürekli ilerlerken istenen zamanda yazma izni vererek bus'ta bulunan değeri yazdırmak. Fakat değeri alsa da sonrasında sanırım yazma izni devam ediyor ve değer almaya devam ediyor. Bu nu nasıl engelleyebilirim. Bu entegreyi başka bir alanda toggle ile denedim orda bir sorun yaşamadım. Fotoğraflar ile daha iyi anlaya bilrsiniz.