Gecmiste cok yanlis yonlendirilmisiz. Belki de yazarlarin okuz altinda buzag arayisi yuzunden.

Ilk sirada;

Mesela 8 bacakli entegreyi lehimlerken

1,5,8,4,7,3,6,2 seklinde lehimlenirse havya sicakligi cipe uzak noktalardan uygulanacagi icin cipin bozulma ihtimalinin dustugu.

Mantiken evet faydasi vardir. Fakat bugune kadar bu kurala uymadan lehimledigim hic bir cip lehimleme esnasinda isinmadan dolayi bozulmadi.

Ustelik pota, firin ya da sicak havayla lehimlemede de bozulmuyor.

Ikinci sirada

Kisa dalga (2...27Mhz) radyo yapmak cok zordur. PCB kotu cizilirse devre pozitif geribeslemeye nedeniyle osilasyona girer. Bilgisi.

Sirf bu kirli bilgi yuzunden bir kez bile kisa dalga radyo yapmaya tesebbus etmedim.

Simdilerde ise dekuplaj kapasitorleri uzerine kuskularim var. Bir kere kafadan cipin Vdd Vss ayaklari arasina 100nF koymak sart. Bu net ve kesin bir bilgi aksi halde lojik devreler scopla dahi zor farkedilecek voltaj cokmelerinde lojik durumlarini degistirebiliyorlar.

100nya paralel 10n, ona paralel 1n 1uF vs devrenin calismasina olumlu katkisi yok. (Teorik olarak katkisi olacagi uzerinde onlarca satir yazi yazilabilir) Fakat devremizden uzaya yayilacak RF yayilimi azaltmaya yonelik etkileri var.

Gene ayni sekilde MCU nun altina genis bakir sase yuzey olusturmak da devremizin daha iyi islemesine yonelik bir tavsiye degil RF yayilimin siddetini azaltmaya yonelik bir onlem.

Benim en buyuk derdim PWM ile anahtarlanan guc elemanlarinin bulundugu devrelerde ADC ile yapilan periyodik olcumlerde gurultunun PCB cizim teknikleri ile ne kadar azaltilabilecegi.

Tabiki bu durumlarda yollarin nereden hangi malzemelerden gecmesi gerektigi onemli. Ama gercekten de en temel kurallara riayet edilerek cizilmis PCB de sinyaller ADC ile nasil daha dogru olculebilir konusunu deneyimleyerek gormeyi cok istiyorum.

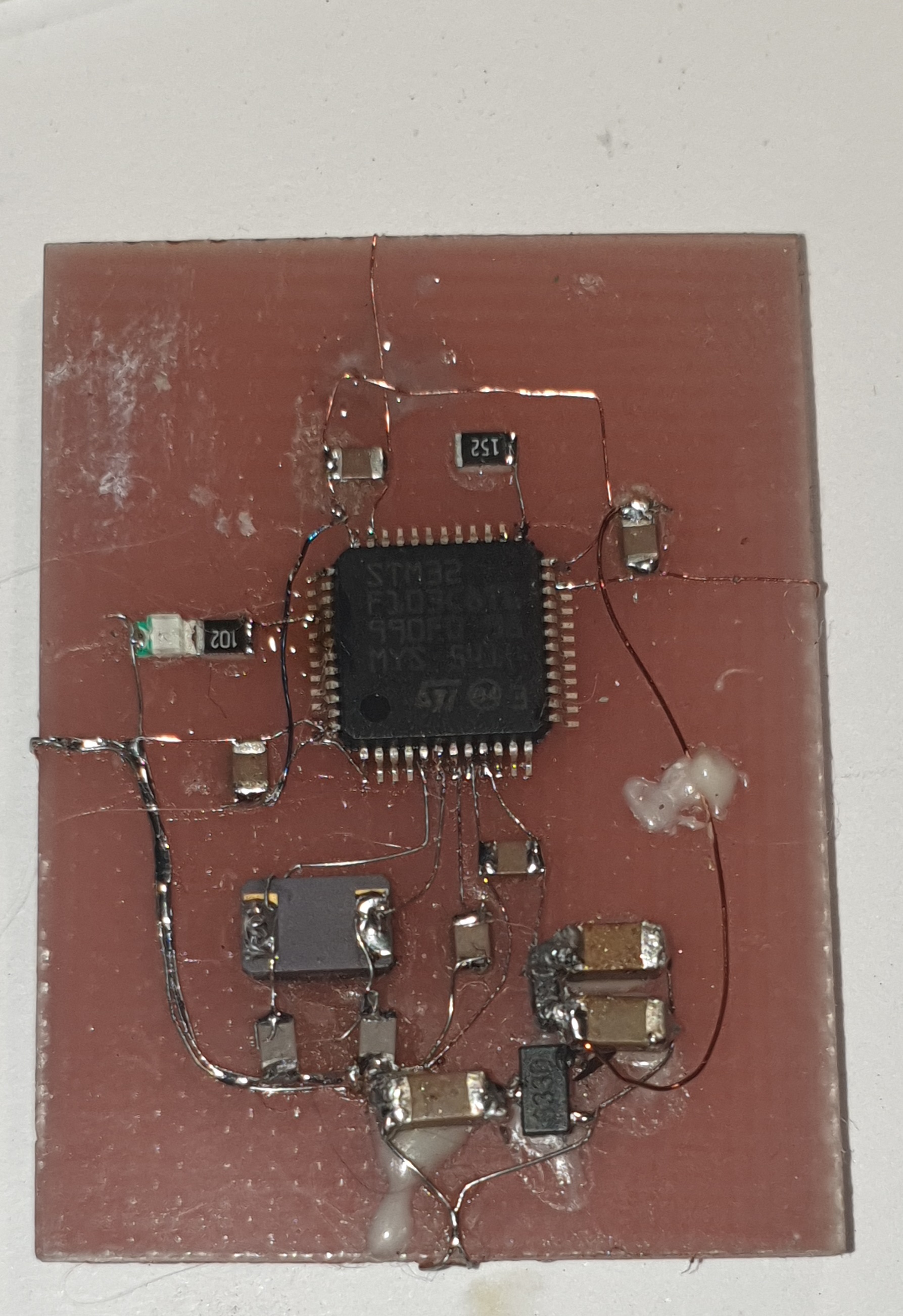

Mesela asagidaki devrede yildiz noktasi olusturarak ADC olcumlerinde gurultu gercekten azalacak mi merak ediyorum.

Normalde bu devrede alt yuzu komple GND yuzeyi olusturuyor ve GND gerektiginde bu GND yuzeyinden baglanti yapiyordum.

Ilk kez bu denli belirgin bir yildiz noktasi olusturdum.

Yapacagim test su sekilde olacak.

ADC girisine 10K//10K gerilim bolucu uzerinden 3.3V/2 gerilimini girip atiyorum 1024 yada daha fazla olcum yaptiracagim.

Ideal bir olcum sonucunda 12 bitde, 1024 olcum yaptiysam bunun 1024 tanesinin de 0x800 olmasini beklerim.

Fakat boyle bir sonuc olmayacagi acik ve net.

Olculen degerleri grafige doktugumde 0x800 merkez olacak sekilde cok dar bir can egrisi grafigi olusmasi lazim. Bu can ne kadar dar ise devrem o kadar guzel sonucuna varmayi bekliyorum.

Bu deneyi en basta verdigim PCB siz telli devrede, yildiz noktali devrede, daha onceki genis GND yuzeyli PCB devrelerimde bir de Bluepill de tekrarlayip bir sonuca varmayi planliyorum.

bunlar sorunları azaltabilir ama bunları yaptım emc konusu bitti gitti diye birşey de yok emc çok kapsamlı ve tecrübe isteyen bir konudur

bunlar sorunları azaltabilir ama bunları yaptım emc konusu bitti gitti diye birşey de yok emc çok kapsamlı ve tecrübe isteyen bir konudur